modeling - UPPAAL: Invariants violated but none have been explicitly set - how to resolve deadlock? - Stack Overflow

modeling - UPPAAL: Invariants violated but none have been explicitly set - how to resolve deadlock? - Stack Overflow

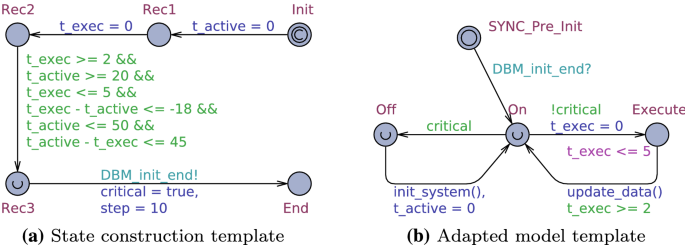

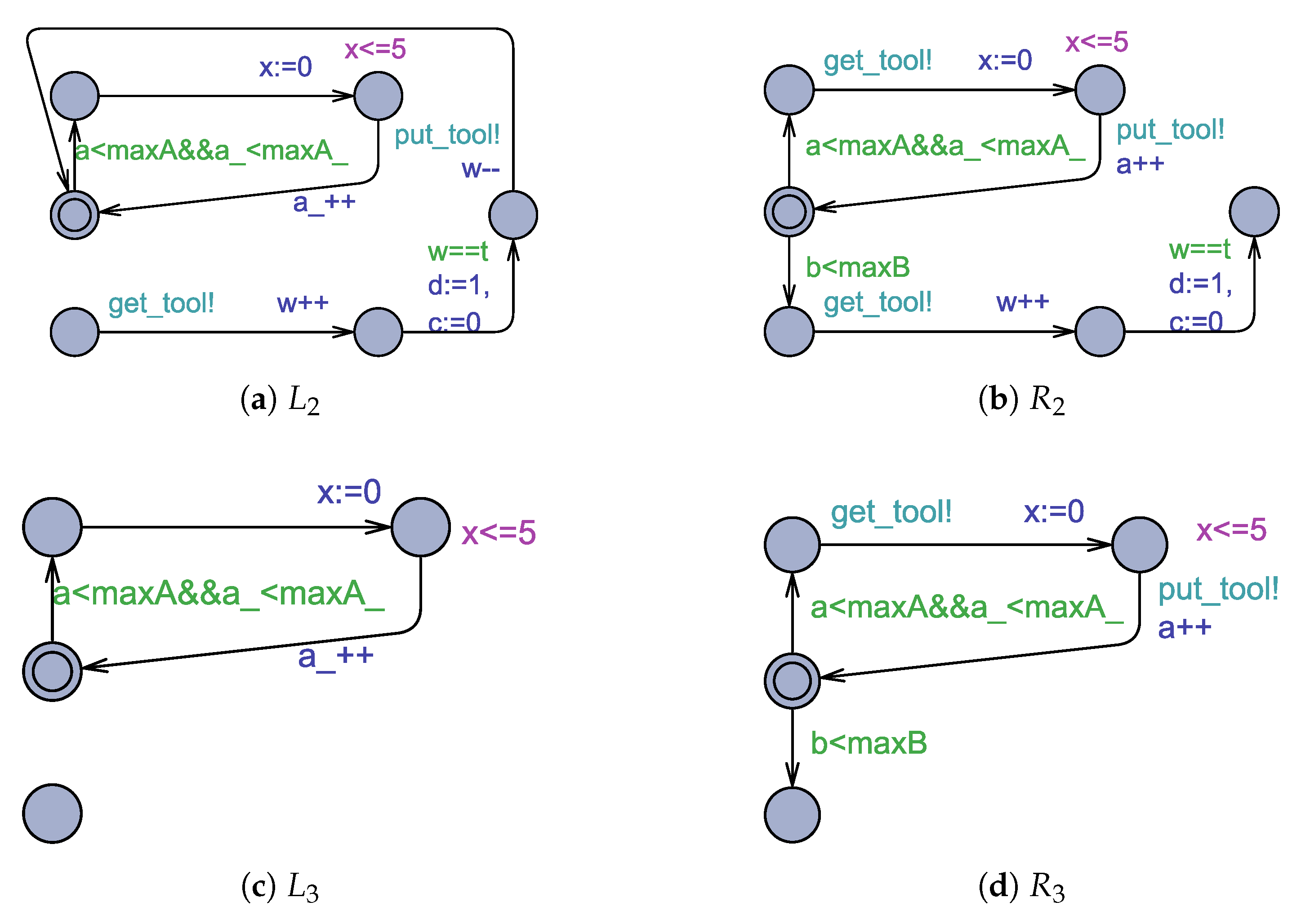

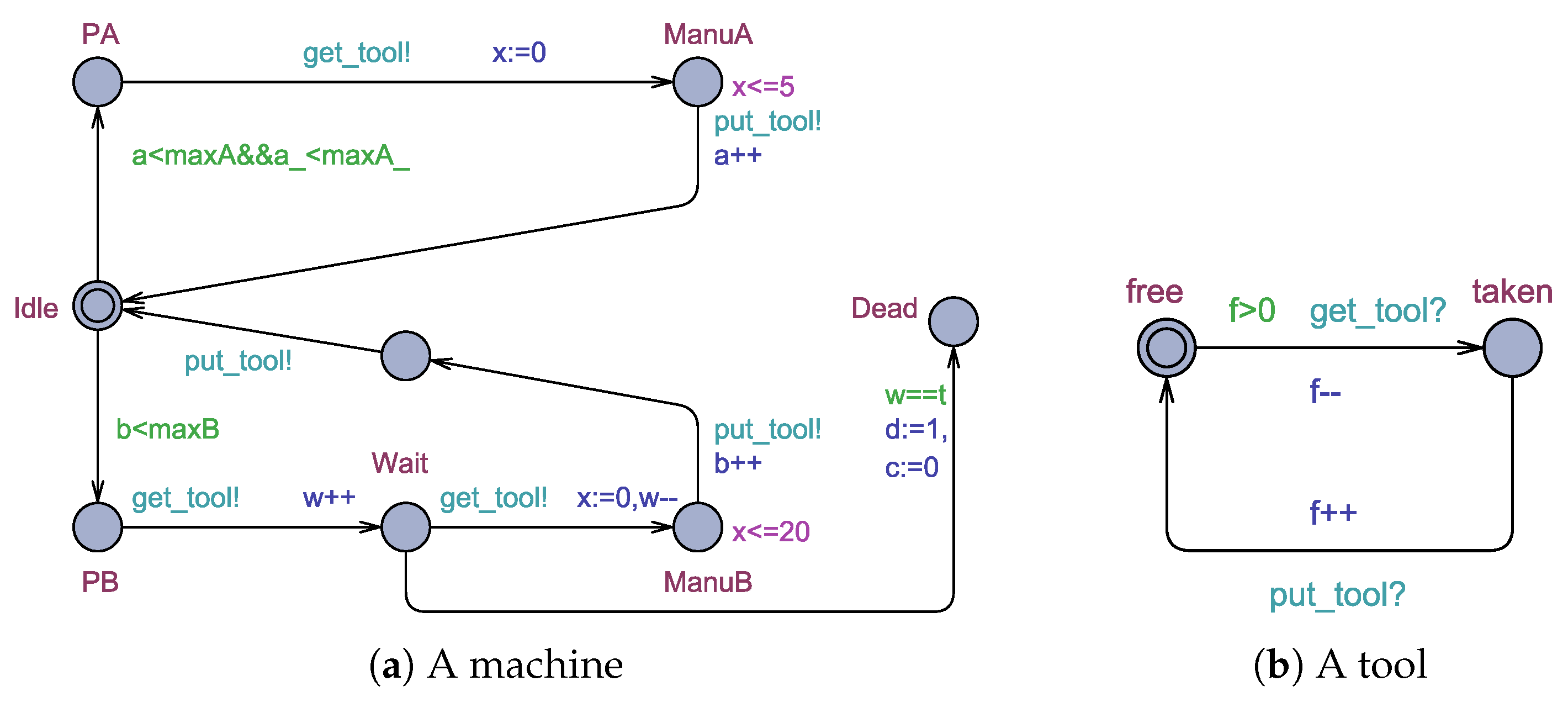

Axioms | Free Full-Text | Dynamic Timed Automata for Reconfigurable System Modeling and Verification

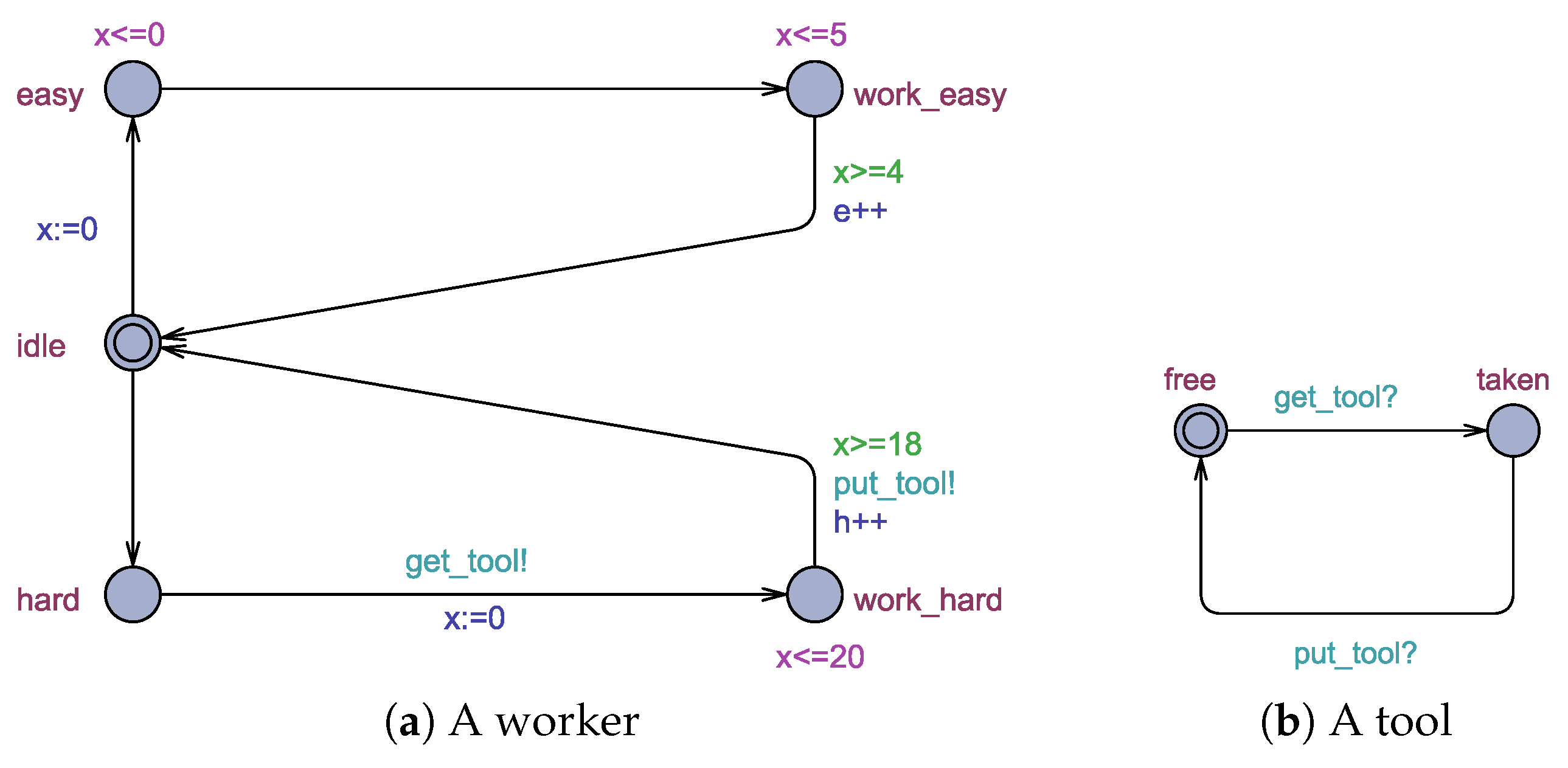

Example of a timed automaton in UppAal. A timed automata may contain an... | Download Scientific Diagram

Axioms | Free Full-Text | Dynamic Timed Automata for Reconfigurable System Modeling and Verification